Regarding the difference between RISC and CISC, there have been some bits and pieces of understanding before, here again to summarize, in order to go deeper.

Representatives of the CISC architecture: x86, C51

RISC architecture code: arm, mips, powerpc, avr, pic

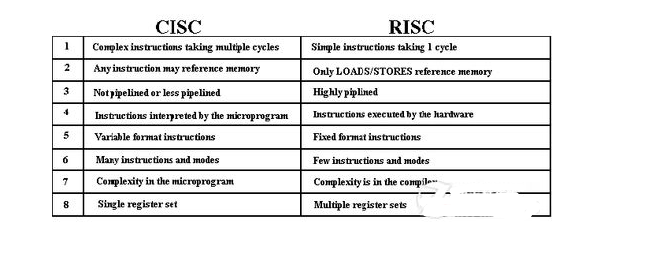

The difference between instruction sets

First of all, it can be understood from the literal understanding that the number of instructions in the CISC (Complex InstrucTIon SetComputer) architecture is definitely far more than the RISC (ReducedInstrucTIon Set Computer) architecture. In addition, under the RISC architecture, the lengths of different instruction opcodes are equal, and the lengths of different instructions under x86 are very different.

Register difference

The CISC architecture generally provides a general-purpose register a (eax under x86) to support most of the arithmetic instructions. However, because the instructions are too complicated, not all registers can support all the operations of the instructions, so there will be Various mov operations for eax affect performance.

Clock cycle required for instruction execution

In the CISC architecture, the clock cycles required for different instructions are different (for example, the periods of multiplication and addition are unlikely to be the same). With RISC architecture processors, most of the instructions can be completed in one clock cycle, which should reduce the complexity of the instruction pipeline design. Many complex instructions of the CISC architecture are implemented by microcode in the CPU, so that the more complex instructions of the microcode require multiple clock cycles to complete. Different clock cycles required for instruction execution increase the difficulty of instruction pipeline optimization.

Access memory difference

RISC is a load/store architecture in structure design. Only load and store instructions can access memory. Data processing instructions only operate on the contents of registers. In order to speed up the operation of the program, RISC sets multiple sets of registers and specifies special-purpose registers. The CISC architecture allows data processing instructions to operate on memory, so fewer registers are needed. In addition, the X86 architecture supports cpu access to unaligned memory addresses, which typically causes CPU exceptions in RISC-based processors. In fact, like the function of non-aligned memory address access, X86 is also realized by the microcode in the CPU, and the efficiency will be greatly reduced.

Addressing mode and IO space

The IO space and the memory space are separated under the X86 architecture, and the IO space is accessed (in, out) using completely different instructions. The RISC architecture does not distinguish between IO space and memory space. It directly maps the IO space to the memory space and directly operates in the memory space. The addressing mode is also simplified in the RISC architecture, and almost all instructions use register addressing.

Compilation difference

The rich advantages of CISC's instructions make it possible for the compiler to do a lot less, and the compiler design is simpler. When RISC implements a function, the number of instruction entries required will be more and the program will be larger.

to sum up:

Compared with the CISC architecture, RISC is a relatively new technology. Because it has no historical burden and does not need to consider backward compatibility, its design can be quite simple and elegant. The RISC architecture's instructions, registers, and pipeline features make it ideal for parallel computing. Can be met, the future RISC architecture will be more and more brilliant.

Gear Sensor has been widely used in the automotive and industrial field, which is important to the measurement of velocity, angel, angular velocity, direction of rotation.

Gear Sensor,Custom Gear Sensor,Gear Sensor 3 Pins,Good Gear Sensor

Yuheng Optics Co., Ltd.(Changchun) , https://www.yuhengcoder.com