Zhu Xiaolin, Zhang Jian, Li Nan, Center for Space Applications Engineering and Technology, Chinese Academy of Sciences

Keywords: VxWorks; SPARC V8; exception handling; address unalignment

1 Overview

VxWorks operating system is an embedded real-time operating system designed and developed by WindRiver, USA. It is widely used in communications, military, aviation, aerospace and other real-time applications due to its good reliability and excellent real-time performance. In the field. VxWorks supports multi-task scheduling with priority preemption. There is no strict distinction between kernel mode and user mode. Context-switching delay during task scheduling is small. It supports board support packages (BSPs) for multiple CPU architectures while providing fast and flexible ANSI compatible IO system for user programming. Based on these advantages, VxWorks has been more and more widely used in aerospace and control applications, such as the US F-16, FA-18 fighter jets, B-2 stealth bombers, and Patriot missiles, and even Mars landing on the surface of Mars. VxWorks is also used on the detectors.

SPARC stands for "Scalable Processor ARChitecture" and is one of the RISC microprocessor architectures. Its design goal is to optimize compilation and better implement hardware pipeline. SUN and TI co-developed the RISC microprocessor-SPARC in 1987, which was the first microprocessor with expandability in the industry. The AT697F used in this paper is a high-performance, highly-integrated SPARC V8 processor. Its implementation is based on ESA's LEON2 processor as a template, and it has been successfully applied to China's space program.

Based on SPARC's unique register window mechanism, an exception handling strategy based on VxWorks is proposed in this paper. Based on this strategy, the exception handling of memory address unaligned access is implemented and verified on the AT697F processor.

2 SPARC register window mechanism and exception handling strategy

2.1 SPARC Register Window Mechanism

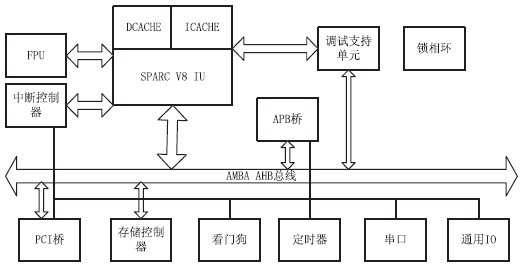

The AT697F processor has 8 register windows, a 5-stage pipeline, a 16-Kbyte 2-way set-associative data cache, a 32-byte 4-way set-associative instruction CaChe, and a floating-point data type that supports double-precision floating-point data types. Processing unit. Supports on-chip peripherals such as PROM, SRAM, SDRAM, and I/O mapped memory access controllers, two 24-bit timers, one watchdog, three serial communication interfaces, and four programmable interrupts Controller, 32 general-purpose IO interfaces, 33MHz PCI interface, etc., at the same time has a complete three-mode redundant design, EDAC and parity, functional interface is perfect, can well meet the needs of aerospace control. The overall block diagram of SPARC is shown in Figure 1.

Fig. 1 Block diagram of SPARC

The register window is a very important concept in the SPARC V8 architecture processor. The register accessible by each register window includes 32 non-floating registers: (input register) in0-in7, (output register) out0-out7, (global register) global0-global7, (local register) local0-local7. According to the actual situation, the number of windows can be 2~32 (NWINDOWS). When the program is called, the output register of the calling program becomes the input register of the called program. The input and output registers are mainly used to pass parameters to the subroutine and receive the subroutines. Run the result and trace the memory stack. The local register is used to store temporary values. The global register does not belong to any window and is used to store global variables. This design can significantly reduce time-consuming memory access instructions and significantly improve instruction performance.

The Processor State Register (PSR) is the most important IU-related internal register. The lower 5-bit CWP forms a pointer to the current window. This register also enables and disables traps, enables coprocessors and floating-points. The processor, and the level at which the specified processor will accept the trap. The Window Invalid Mask register (WIM) determines whether a SAVE, RESTORE, or RETT instruction will generate a window overflow or underflow trap. WIM[n] corresponds to the register bank with CWP=n. WIM[n]=1 means the window is invalid, WIM[n]=0 means the window is valid. The AT697F processor has eight register windows, so the value of W8-W31 is always 0, and the initial value of W0-W7 is 0, but it will change as the program runs.

When the SAVE instruction is executed, the hardware automatically compares the new window (CWP-1) mod nWindows with the window invalid mask register WIM. If the new window is invalid, ie, WIM[CWP-1]=1, an overflow trap will be generated. Call the windowOverflow exception handler.

The CWP is increased when the RESTORE and RETT instructions are executed, and (CWP+1)mod nWindows is compared with the window invalid mask register. If the new window is invalid, an underflow trap will be generated and the windowUnderflow exception handler will be called. It should be noted that the CWP is also decremented by 1 when trap occurs, but window overflow check is not performed.

windowOverflow is a window overflow trap handling function caused by the SAVE instruction. The exception post processing flow is as follows:

(1) The hardware sets CWP to (CWP-1)mod nWindows and enters this exception handling function.

(2) The WIM register is cleared, and then the CWP-1 window register is saved.

(3) Set WIM[CWP] to zero and WIM[CWP-1] to 1. Even if the CWP window is valid, the CWP-1 window is invalid.

(4) Jump back to the SAVE instruction that caused the trap to continue execution.

First of all, it is known that WIM is changed by software. When the software is initialized, WIM[1] is set to 1 and CWP is set to 0. In this way, each time a function call is made, CWP becomes (CWP-1)mod nWindows, when CWP is subtracted. When you continue to 2 SAVE will trigger a windowOverflow, because WIM[1] = 1, and then in the windowOverflow function will want to set WIM[1] to 0, and at the same time save the CWP = 0 window, the WIM [0] Set to 1, setting window 1 to active, and window 0 to invalid. This design ensures that when the function call depth is greater than the number of windows, the contents of the window registration can be saved to the stack.

The windowUnderflow function is a window underflow trap handler caused by the RESTORE instruction. The exception handling process is as follows:

(1) The hardware sets CWP to (CWP+1)mod nWindows and enters this exception handling function.

(2) Clear the WIM register and RESTORE twice (note that the CWP will be automatically decremented by 1 after the exception is generated) to restore the CWP+2 window register.

(3) Set WIM[CWP+3] to disable the CWP+3 window.

(4) Jump back to the RESTORE instruction that caused the trap to continue execution.

WindowOverflow and windowUnderflow two functions cleverly cooperate to complete the scene recovery and save the depth function call, making the function can be called in depth, which is the core of the SPARC register window mechanism, the memory access address after the completion of non-aligned exception handling is based on The mechanism is completed.

However, it can be seen that when the depth of the function call is greater than the number of windows, the register site will be stored in memory, which will reduce the efficiency of the function call, so the efficiency of the program can be improved by minimizing the call depth of the function.

2.2 SPARC-Based VxWorks Exception Handling Strategy

There are many reasons why SPARC V8 generates exceptions, such as program breakpoints, divide-by-zero exceptions, data access exceptions, write memory errors, bus exceptions, and load instruction exceptions. Normally, after an exception is generated, the current task that generates an exception is stopped, and an error is reported through the function interface to notify the upper application program. If the process is not timely, the system may crash and crash. This is not allowed in a highly reliable system.

According to the SPARC Architecture Manual manual, SPARC V8 includes two types of traps: default exception handling and enhanced exception handling. Default exception handling is a generic exception handling that applies to all types of exceptions. Enhanced exception handling is based on the default exception handling, and the user installs specific exception handlers. This article treats address non-aligned processing as enhanced exception handling, user-customized exception handlers, and installs them into exception vector tables to implement personalization.

The core of exception handling has two things: processing and recovery. The text adopts the hook function mechanism. The exception handling function is hooked into the exception handling hook function when the system is initialized, and is triggered by the system exception. The function of this function is to perform on-site saving and user-defined processing, and then call the exception recovery function. Processing and recovery functions are handled differently depending on the hardware and software environment.

For VxWorks5.4 operating system, after the CPU detects an exception, it jumps to the corresponding vector table, first executes the excEnter assembly function, performs window detection before exception handling, saves the job on site, and then calls the excExcHandle function, which is a C language. The implemented functions facilitate upper user hooking hook functions and personalizing different traps.

3 address unaligned exception handling

When a processor reads or writes a memory data unit, the destination address must be an integer multiple of the number of bytes of the accessed basic data type. This is called address alignment. If a non-aligned address is accessed, the CPU will trigger an exception. Architectures such as ARM, POWERPC, and SPARC do not support unaligned address access.

Take AT697 as an example, the address of the unaligned exception vector is 0x7, and the address unaligned exception is caused by the following situations:

(1) SPARC stipulates that the halfword is two bytes, the word is four bytes, the doubleword is eight words, and the load/store memory operation instruction, when the read or store halfword instruction is executed, the memory address is not two characters. Section alignment, the memory address is not four-byte aligned when a read or store word instruction is executed, and an exception occurs if the memory address is not eight-byte aligned when a read or store double-word instruction is executed.

(2) This exception is generated when the address to which the JMPL/RETT instruction jumps is not four-byte aligned.

Under normal circumstances, a non-aligned SPARC address exception will result in the termination of the current task. In order not to prevent the current task from continuing, access to unaligned addresses continues. The first exception can be handled as follows: Unaligned address stripping Divide into two alignment visits, and concatenate the two data to complete access to unaligned addresses. The second case can be considered as the address unalignment caused by the address bit flipping in the jump instruction. The AT697F core register group adds a three-mode redundancy function to prevent bit flipping, and the EDAC check can correct a register or memory data error. If you encounter this kind of anomaly, you can try to force the lower two bits of the jump address to be zeroed to force alignment.

Take the 4-byte unaligned address read operation as an example. Disassembly shows that the instruction that generated the exception is ld [%o0], %o1, where %o0 is a non-four-byte aligned memory address. If this statement is executed, a memory address not aligned exception will be generated. The exception vector number is 0x7. The CPU will jump to the specified position in the exception vector table. The processing is as follows:

(1) Execute excEnter to save the abnormal scene to the ESF structure (including PC, NPC, etc. that generate abnormal instructions), and determine whether the current WIM[CWP] is 1, and if it is 1, clear it to 0, and The register of the CWP-1 window is saved to its own stack and WIM[CWP-1] is set to 1.

(2) Jump to the excExcHandle function. This function is implemented in the C language. It has a generic exception handling function that can notify upper-level users or print exception information.

(3) For the address non-alignment exception, call its own defined good initialization function func excHandler. This function is implemented by assembly. If the address to be read is 0x8000,0001, the function will address 0x8000, 0000 and 0x8000 respectively. , 0004 two read operations, and shift, splicing read 32-bit data 0x8000,0001 address.

(4) After reading the data, you need to restore the content of the abnormal scene. Here, select the previous window CWP+1 as the restoration window, because this window is just called, it must be a valid window, you need to The scene before generation is restored to the CWP+1 window, and the read 32-bit data is restored to the %o1 of the CWP+1 window, and then returned to the NEXT PC address to continue execution.

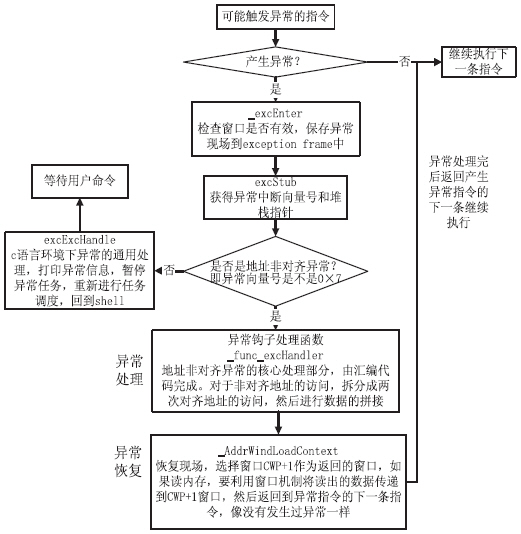

After the code modification is completed, it is necessary to recompile the VxWorks library file, generate a new library file code, and then recompile the new kernel. The specific code and steps will not be described in detail. The address non-aligned processing flow is shown in Figure 2.

Figure 2 address unaligned processing

4 Experimental verification

Load the following test program into the kernel.

Void excTest2()

{

Char buff[8] = {0x12, 0x34, 0x56, 0x78, 0x9a, 0xbc, 0xde, 0xf0};

Int v32=0;

Int *p32=NULL;

P32=(int*)&(buff[1]);

V32=*p32;

}

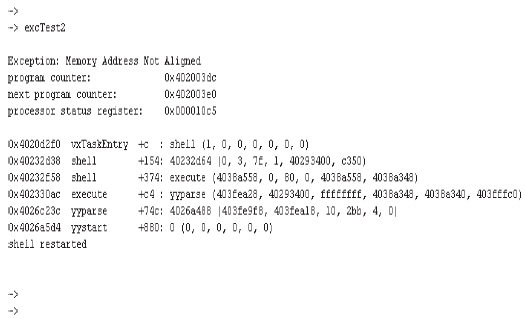

The original intention of the program is to read 0x3456789a four bytes. Obviously, the four-byte starting address of this function is a non-four-byte aligned address, perform a four-byte read operation on it, and run excTest before adding exception handling. The function will report the exception shown in Figure 3.

Figure 3 Exception Report

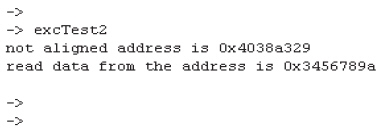

After adding the exception handler, the result of the operation is shown in Figure 4. As if no exception occurred, 0x3456789a data was correctly read and the test was successful.

Figure 4 Operation result

5 Concluding remarks

The perfection of exception handling strategies has a very important impact on highly reliable embedded systems. Exception handling under the SPARC architecture processor needs to make full use of SPARC's unique window mechanism, which can greatly improve the efficiency of exception handling. Combined with the advantages of embedded real-time operating system VxWorks, it can greatly improve the stability and reliability of the system.

The exception handling of address unaligned access is not implemented on many CPUs. Although the implementation is not the same on different CPUs, the core mechanism is the same. The exception handling policy in the text can also be applied to other CPU exception handling.

Disposable Vape Devices-- Classic

AURORA SERIES DISPOSABLE VAPE PEN

Zgar 2021's latest electronic cigarette Aurora series uses high-tech temperature control, food grade disposable pod device and high-quality material.Compared with the old model, The smoke of the Aurora series is more delicate and the taste is more realistic ,bigger battery capacity and longer battery life. And it's smaller and more exquisite. A new design of gradient our disposable vape is impressive. We equipped with breathing lights in the vape pen and pod, you will become the most eye-catching person in the party with our atomizer device vape.The 2021 Aurora series has upgraded the magnetic suction connection, plug and use. We also upgrade to type-C interface for charging faster. We have developed various flavors for Aurora series, Aurora E-cigarette Cartridge is loved by the majority of consumers for its gorgeous and changeable color changes, especially at night or in the dark. Up to 10 flavors provide consumers with more choices. What's more, a set of talking packaging is specially designed for it, which makes it more interesting in all kinds of scenes. Our vape pen and pod are matched with all the brands on the market. You can use other brand's vape pen with our vape pod. Aurora series, the first choice for professional users!

We offer low price, high quality Disposable E-Cigarette Vape Pen,Electronic Cigarettes Empty Vape Pen, E-cigarette Cartridge,Disposable Vape,E-cigarette Accessories,Disposable Vape Pen,Disposable Pod device,Vape Pods,OEM vape pen,OEM electronic cigarette to all over the world.

Disposable Pod Vape,Disposable Vape Pen,Disposable E-Cigarette,Electronic Cigarette,OEM vape pen,OEM electronic cigarette.

Shenzhen WeiKa Technology Co.,Ltd. , https://www.zgarecigarette.com