With the development of the economy, people’s safety awareness is constantly increasing, and the demand for video surveillance equipment is also continuously increasing. At the same time, in this area, the competition of equipment manufacturers has become increasingly fierce. It is estimated that there are more than 1,000 monitoring equipment suppliers in the world, and emerging companies in China, South Korea, and Taiwan are gradually entering the global competition. Some manufacturers have started to export their products to the North American and European markets.

The intensification of competition has further promoted the development of product technology. Leading vendors often rely on advanced video compression algorithms and intelligent image analysis capabilities to enhance the competitiveness of their products. In general, the technical development trend of video surveillance can be summarized as the following: The new H.264 compression technology has gradually become mainstream, and adopting H.264 technology can increase the storage time of the hard disk, and at the same time reduce the demand for network bandwidth; High-definition (HD) video systems are starting to appear in some high-end applications and will gradually expand to mid-to-low-end applications; PCI Express is replacing the traditional PCI bus, and many of the current popular PCI compression cards will also be converted to PCI Express bus Architecture; With the popularity of IP networks, IP-based video surveillance systems have grown rapidly.

All of the above changes require the use of devices with higher performance and flexibility to build video surveillance products. In the past, simply using a DSP processor or off-the-shelf chip (ASSP) approach has been difficult to meet the system requirements, while the programmable logic gate array (FPGA) The unique flexibility and high performance make it an ideal solution for many monitoring products.

Below we will discuss how to implement some typical video surveillance products using Altera's FPGA products and video solutions. These products include soft-compressed digital video recorder (DVR) cards, hard-compressed multi-channel DVR systems, and popular IP network cameras.

Digital Video Recorder

In the DVR field, users can choose soft compression or hard compression. The so-called soft compression refers to the use of PC or IPC platform to compress single or multiple video, and further processing by the PC (such as storage or transmission over the network). Hard compression refers to the use of hardware to achieve video compression, and then directly stored or transmitted over the network. The hardware here refers to DSP processors, media processors, and FPGA devices.

Compression algorithms such as MPEG-2 and MPEG-4 are usually performed using soft compression, while high-complexity compression algorithms such as H.264 can only be implemented by hardware. H.264 D1 resolution compression can usually be implemented using a DSP processor, DSP+FPGA, or a single low-cost FPGA, such as the Cyclone series and the Arria GX series. From the aspects of cost and ease of implementation, high-end Stratix series FPGAs are more suitable for H.264 high-definition resolution compression.

Soft compression DVR

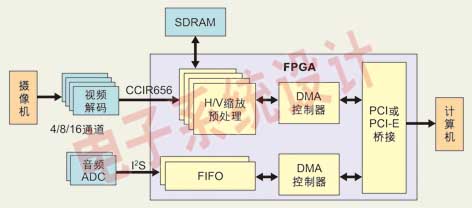

Figure 1 shows a functional block diagram of a software-compressed DVR. Most of the functions implemented in Figure 1 have low logic complexity. At the same time, they have certain requirements for data path performance and require high-speed interface communication capabilities. Therefore, they are very suitable for implementation with FPGA devices.

Figure 1: The functionality of a soft-compressed DVR is well suited for implementation with FPGA devices.

The scaling and other pre-processing tasks (such as video filtering), DMA controllers, audio FIFOs, and PCI-E sections can all fit into the FPGA. The advantage of using an FPGA is that it can flexibly implement any multi-channel video input. At the same time, the function of the video pre-processing section can be flexibly customized according to the characteristics of different cameras to achieve optimal results.

Altera's Video Image Processing Suite (VIP) includes nine video pre-processing/post-processing IPs, including Scaler, 2D FIR filtering, and other IP. The PCI and PCI-E IP cores at the interface are also Altera's off-the-shelf solutions.

The latest 65nm low-cost FPGA Cyclone III has a great advantage in terms of power consumption, and an external 2.5Gbps transceiver chip is required to implement the PCI-E interface. The use of low-cost Arria GX FPGAs with embedded transceivers offers advantages in terms of integration, giving users the flexibility to implement the device.

2. Hard compression DVR

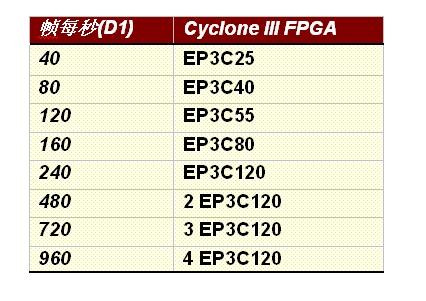

Multiple hard-compressed DVRs are also an important part of the video surveillance system. Typical channel numbers include 4, 8 and 16 channels, and some products even exceed 24 channels. The core of the system is multi-channel video compression. Unlike traditional ASSP or DSP implementations, FPGAs provide a more flexible, scalable solution with lower single video costs and lower power consumption. Cyclone III Single The chip can support up to 16 channels of H.264 encoding. Table 1 lists the benchmarks when using Baseline H.264 D1 resolution encoding compression with Cyclone III.

Table 1: H.264 D1 encoding with Cyclone III FPGAs.

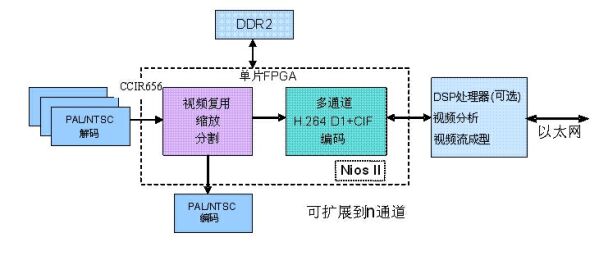

In a typical multi-channel DVR system, multi-channel analog video is first converted to standard CCIR656 format data after analog-to-digital conversion. In order to monitor the multi-channel picture locally, it is usually necessary to multiplex the multi-channel video data and partition the picture. Therefore, the video zoom function is required. The rich M9K memory resources in Cyclone III devices are very suitable for use as a video scaling algorithm. The line cache, as shown in Figure 2. The scaling and line buffering in Altera's video image processing suite helps users quickly implement picture multiplexing and segmentation capabilities.

The multi-channel "H.264 D1+CIF" encoding is the core of the entire system. The inherently powerful parallel processing capability of the FPGA meets the H.264 algorithm's requirements for processing speed and is the only single-chip solution that can be implemented. Single-chip FPGAs provide more stable system performance, lower cost, and the best price/performance ratio compared to multiple ASSP or DSP processor implementations. At present, Altera Corporation has jointly launched a multi-channel "H.264 D1+CIF" solution with a third-party company.

In addition, it is also possible to add a DSP chip in some systems to implement functions such as bitstream analysis, video stream generation, or audio compression that do not require high real-time performance and parallel processing to fully exploit the respective advantages of FPGAs and DSPs.

IP camera

The IP camera is the fastest growing product in the field of video surveillance. The IP camera can preprocess and compress the video source obtained by the camera and then perform remote transmission or remote storage over the IP network. Its important components include video preprocessing, video compression module, and IP network video (Video -Over-IP) function.

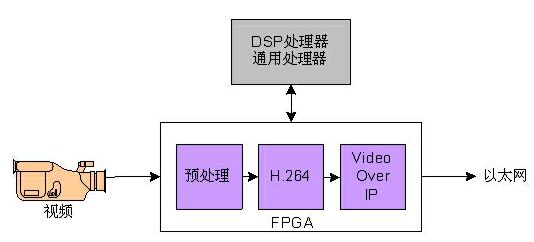

The input data format of the current mainstream IP camera is: 1 D1/25 frames per second + 1 CIF/25 frames per second. Usually can use a slice of Cyclone II EP2C35 and a low-cost processor to realize, the function is shown as in Fig. 3.

Figure 3: Standard definition D1 IP camera.

As the resolution of the current IP camera is gradually evolving from SD (D1) to HD (1,280×1,024), and local real-time compression is necessary, only hardware compression can be used. If multiple DSP processors are used, the system's cost, integration, and power consumption will be unacceptable to the user. Single-chip low-cost FPGA performance can not meet the design requirements.

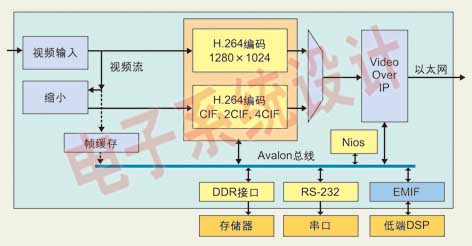

At this point, monolithic high-performance Stratix series FPGAs naturally become the preferred solution. Stratix FPGAs have a corresponding structured ASIC, the HardCopy family of devices, that can help users further reduce costs by one-tenth and reduce power consumption by 50%. Figure 4 shows the functional modules of a single HD IP camera.

Figure 4: Functional block diagram of a single HD IP camera.

Similarly, video input preprocessing (including filtering, scaling, and other functions) can be implemented using Altera's VIP suite. The "1,280 x 1,024/25 frames per second + 1 CIF/25 frames per second" H.264 video compression engine will be implemented in the FPGA hardware and can be provided by a third party partner of Altera Corporation. The Nios II processor and VoIP reference design help users map video to IP networks and transmit them over Ethernet.

In addition, a low-cost DSP processor can assist in the work of video stream analysis. These operations have complex logic relationships but do not require high performance.

Altera's custom on-chip bus Avalon and SOPC Builder system integration tools help users automate and interconnect the required peripherals, greatly improving design efficiency.

This article summary

The rapid development of the video surveillance market has rapidly promoted the use of FPGAs in this area. Some new technical directions, such as multi-channel, high-definition, networking, and high-speed communication interfaces, have promoted the further development of FPGAs in the field of video surveillance. At the same time, advances and updates in FPGA chip technology, IP cores, and reference designs have also promoted and catered to the needs of the industry. Altera's continuous attention and investment in the video surveillance market is precisely to seize this opportunity to create more value for users.

Lc Fiber Coupler,Lc To Sc Coupler,Sc To Lc Coupler,Mpo To Lc Adapter

Ningbo Fengwei Communication Technology Co., Ltd , https://www.fengweifiberoptic.com