This paper takes the bank's existing queuing system as an example, and proposes the interface design of the MCU queuing system of the IIC bus. Through the simulation test of the system, it not only simplifies the design circuit, reduces the circuit board area, saves the components in the conventional design, and reduces the use. Various costs, as well as system energy consumption, noise cancellation, reliability and other performance are improved. In the MCS-51 series MCU without the IIC bus interface composed of data measurement and control and intelligent instrumentation, the interface device type of the system can be increased through the IIC bus. Reduce system cost and improve application system performance [1-3].

1 IIC bus

The IIC bus (Inter Integrate Circuit Bus) is a bidirectional two-wire bus consisting of a serial clock line (SCL) and a serial data line (SDA). The two wires are connected to different devices with IIC bus. Data transfer between devices, data transfer rate in high-speed mode up to 3.4 Mb / s, not only simplifies the circuit design and improve the efficiency of hardware use, so that the IIC bus is widely used in the serial transmission design of embedded systems, currently mainly used Digital control systems such as central control centers, audio integrated circuits and video.

1.1 IIC bus timing

(1) start and stop

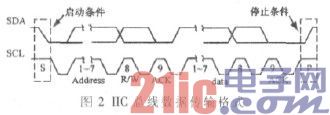

When the bus is not busy, the clock and data lines remain high. The start condition (S) is when the clock line is at a high level and the data line is at a falling edge. The stop condition (P) is when the clock line is at a high level and the data line is at a rising edge, and the IIC bus starts and stops as shown in FIG. .

(2) Data transfer

The transmission of one data bit requires one clock pulse, and one flag bit is added after every 1 B. When the flag generated by the transmitter is high level, the master device generates an additional flag bit clock pulse. The information on the data line SDA should be kept stable only when the clock pulse is high, otherwise the data on the data line SDA will become the control signal, as shown in Figure 2.

(3) IIC bus protocol

Before the IIC bus transmits data, it should indicate the address of the received device. When the IIC bus is started, this address is transmitted together with the 1st transmitted byte.

In this system, the PCF8563 chip acts as a slave transmitter or a slave receiver. The SCL signal line is only an input line, and the SDA data line is a two-way signal line.

1.2 Chip PCF8563 Overview

PCF8563 is a classic low-power real-time clock/calendar chip [4]. It has IIC bus interface technology. The maximum transfer speed of the bus can reach 400 kb/s. After each write and read data, the internal word address register will be automatically incremented. It has the characteristics of low power consumption and high precision. PCF8563 has timer function, multiple alarm functions, interrupt output function and clock output function, can complete a variety of timing services, can also realize watchdog technology for single-chip system, its internal oscillation circuit, clock circuit, low voltage 1.0 V Detection circuit and IIC two-wire bus communication method, and solve the problem of 2000, not only make the peripheral circuit and its simplicity, but also increase the reliability of the chip, can be widely used in water meters, electricity meters, mobile phones, portable instruments, fax machines , battery power and other product areas.

2 system design

The tuning fork level switch is also often referred to as the tuning fork level meter or the tuning fork level controller, mainly because the tuning fork level meter appears in different links in industrial production, and actually plays different key roles, so people are habitual called many different names. Tuning fork level switch is a kind of level switch. It mainly uses the resonance principle of tuning fork to measure the level state. Its unique fork body design and its inherent vibration characteristics can ensure the automatic cleaning function of the tuning fork and prevent material hanging to the greatest extent. .

Tuning fork level switch,Marine tuning fork level switch,Fork Tuning Level Switch

Taizhou Jiabo Instrument Technology Co., Ltd. , https://www.taizhoujbcbyq.com